Researchers Demonstrate a New 3D Dram Technology That Increases Memory Density

| 05-09-2022 | By Robin Mitchell

Researchers have conducted an experiment to reduce the size of DRAM and increase memory density by eliminating the need for a cell capacitor, which they achieved through the 3D stacking of vertical transistors. The new technology, called capacitorless DRAM, has been tested using simulation and TCAD to prove its effectiveness. While capacitorless DRAM may present a new solution, planar DRAM still faces challenges, and it remains to be seen whether DRAM will eventually be replaced by alternative storage memory. What challenges does DRAM face, what did the researchers present, and will DRAM eventually be replaced?

What challenges does DRAM face?

Dynamic Random Access Memory (DRAM) is the dominant computer memory technology thanks to its low transistor count (one transistor per cell compared to 6 for SRAM) and high memory density. At the same time, DRAM has been in development for decades, which has helped to overcome some of the technical challenges faced by DRAM, such as the need for refresh cycles. As such, the difficulties of integrating DRAM into computers have now been solved and are almost always handled by some dedicated off-the-shelf memory controller.

And yet, DRAM still presents challenges to engineers when creating computing systems. Even though DRAM offers a higher memory density than other technologies, SRAM still takes the lead in microcontroller designs thanks to its all-transistor design. DRAM also suffers access issues in that the need for refresh cycles can interfere with a typical operation (this is why CPUs will load data in from RAM and store it into an internal cache which often uses SRAM).

DRAM is also a volatile memory meaning that it loses its data contents when switched off. While this may be beneficial from a security perspective, it also means that whenever computers reboot, it has to be from scratch. This also means that any data held in RAM during an unexpected reboot is also lost, hence the importance of frequent saving.

Researchers demonstrate a 3D capacitorless DRAM cell simulation

Increasing the density of semiconductor devices can be done using numerous techniques. By far, the most popular option is to make transistors physically smaller so more can be integrated per unit area. However, not all designs can be easily shrunk, and shrinking transistors introduce additional challenges, such as quantum tunnelling and noise. Another option is to orient parts vertically so that parts stretch upwards instead of outwards. As the planar space on a semiconductor is valuable, this can increase the number of active parts on a die without reducing the size of transistors (in fact, they can often be made larger).

Recognising the advantages of 3D designs (something done frequently in NAND flash memory), researchers recently published a paper on a 3D DRAM technology that not only increases DRAM density but also removes the capacitor entirely.

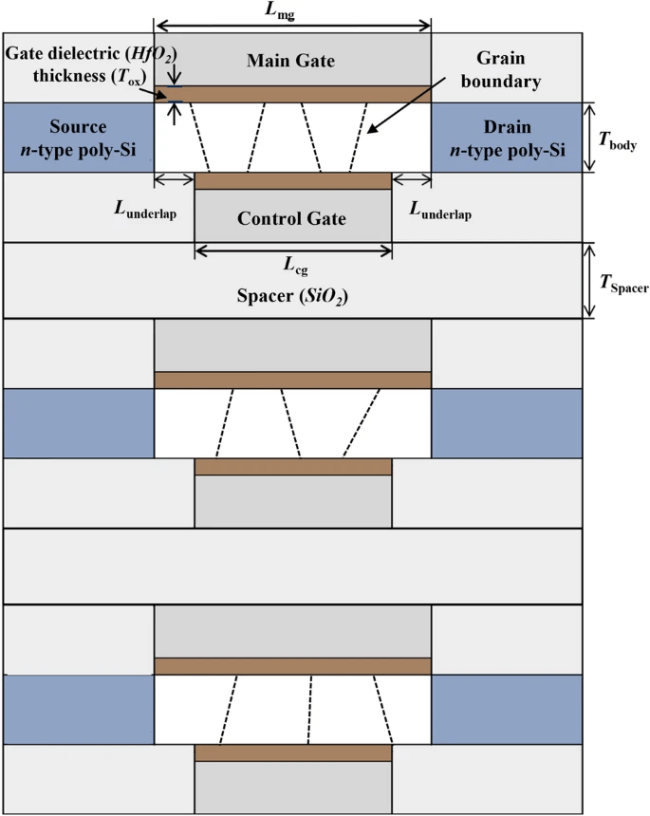

The cross-sectional view of the proposed 3-D stacked ADG poly-Si MOSFET-based 1 T-DRAM cell with an ADG structure.

The new DRAM design comprises just a single transistor to store information, and the use of a polycrystalline silicon metal oxide semiconductor FET with an asymmetric dual-gate structure allows for the floating body effect to store electric charge (instead of needing a large external capacitor).

To test their theory, the researchers took advantage of technology computer-aided design simulation (TCAD) that not only measured the performance of the proposed technology but how key physical elements such as grain boundaries would affect the memory (grain boundaries and crystal orientation have a massive effect on semiconductors). Overall, the researchers determined that their proposed memory, if integrated on a large scale, has the potential viability of being a 1T memory technology.

Will DRAM eventually be replaced?

Like with any technological development, DRAM will eventually be replaced by some superior memory technology developed by advanced human beings in the far future. But with regards to the near future, it is unlikely that DRAM will be replaced any time soon, and this comes down to two factors; its speed and infinite read/write cycle endurance.

Even though SRAM is faster than DRAM, the use of 6 transistors compared to a single transistor and capacitor makes DRAM cheaper (which also translates to increased memory sizes). This means that a computer system can more easily integrate larger memory sizes, something which is becoming ever more important with the introduction of AI and other complex systems into modern computing platforms.

Additionally, the increasing number of cores in modern CPUs sees the need for more cache, and this will see DRAM continue to offer a decent cost-to-performance ratio as the memory from RAM would be loaded in blocks instead of real-time memory access (of course, an entirely SRAM-based system would be faster, but also horrendously expensive). Even if a process requires real-time access to RAM, its operation would block other processes from accessing data; hence DRAM would never be found in such an application.

The ability for DRAM to never wear down during operation also makes it a difficult memory technology to eliminate. Very few memory technologies in existence never wear down, and those that don’t either have very slow access times (such as hard disks) or are expensive to produce on a scale (i.e. SRAM).

Finally, if DRAM can be fabricated without the need for capacitors, it would present engineers with significantly higher memory densities without a price increase. Even though most capacitors are vertically stacked on top of their transistor (in the metal layers), they must be separated from other cells to prevent interference. As such, removing the capacitor allows transistors to be stacked closer together, while the 3D construction will enable transistors to take up less planar space.

Overall, DRAM still presents engineers with an excellent memory option thanks to its ease of manufacture, high endurance, good performance, and low cost.