High-Rise 3D Chips by MIT: Boosting Semiconductor Power

Insights | 17-01-2025 | By Robin Mitchell

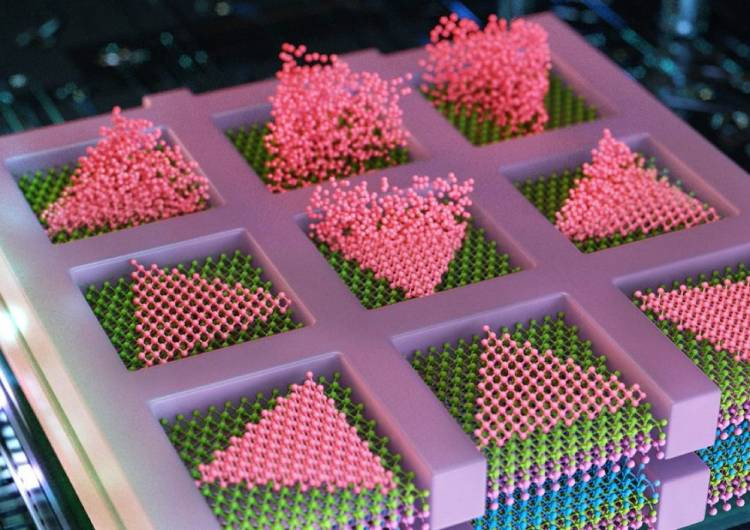

MIT engineers have devised a technique to stack electronic layers seamlessly, producing faster, denser, and more powerful computer chips. Triangular semiconducting particles (pink) are confined within squares to form high-quality elements, layered directly atop other semiconducting materials (depicted in purple, blue, and green). Image: Cube 3D Graphic

While planar transistor designs have long formed the foundation of modern electronics, the relentless push for ever-smaller and more efficient devices has revealed critical limitations in these two-dimensional architectures. Recently, researchers at the Massachusetts Institute of Technology (MIT) have introduced an innovative 3D stacking method that could overcome these challenges by packing more transistors into denser layers, potentially reinvigorating Moore’s Law.

Key Things to Know:

- 3D stacked devices are reshaping Moore's Law: MIT's innovative stacking method increases transistor density and enhances semiconductor efficiency, addressing the limits of traditional planar designs.

- Low-temperature integration: The method operates below 400°C, enabling compatibility with existing silicon-based circuits while reducing energy consumption and thermal stress.

- Revolutionary applications: This breakthrough supports AI, machine learning, and IoT by offering faster communication, higher processing power, and improved energy efficiency.

- Future potential: With ongoing research into scalability and industrial applications, 3D stacked technology could transform computing and extend the relevance of Moore's Law for years to come.

What hurdles do traditional planar devices face, what novel approach have MIT engineers developed, and how might their 3D stacked technology reshape the future of semiconductor performance and efficiency?

How Planar Devices Are Restricting Moore's Law

Transistors have been the backbone of modern electronics since their introduction in the 1950s. Their ability to control the flow of electrical current has enabled the creation of a wide range of electronic devices, from simple amplifiers to complex processors. However, as transistors have continued to shrink in size, they have faced a number of challenges that threaten their continued viability.

Physical Limitations of Shrinking Transistors

One of the major challenges facing transistors is the physical limitations of shrinking them down to atomic scales. At these tiny sizes, quantum mechanical effects such as electron tunnelling and quantum fluctuations become dominant, causing unpredictable and less controllable behaviour. This means that as transistors approach the atomic scale, their behaviour becomes fundamentally different from larger scales, making it harder to control their operation.

Another challenge faced by transistors is the increased leakage current that occurs as they shrink. This is due to the thinning of the gate oxide layer, which controls the flow of electrons in the transistor. As the gate oxide layer becomes thinner, the likelihood of breakdown and leakage increases, leading to reduced efficiency and reliability. Additionally, the decreased control over current flow caused by shrinking the gate length also impacts the overall performance of the transistor.

The Declining Viability of Silicon in Transistors

The use of silicon as the primary material in transistors also presents a number of challenges. While silicon has been the dominant material in the electronics industry for decades, it is now reaching its physical limits in terms of conductivity and electron mobility at very small sizes. As silicon transistors shrink, the efficiency of electron flow decreases due to increased scattering, leading to lower performance. Furthermore, the breakdown of traditional scaling methods means that silicon is no longer able to be shrunk down to smaller sizes while maintaining its electrical performance.

Manufacturing and Design Complexities

In addition to the physical challenges faced by transistors, there are also a number of manufacturing and design-related issues that need to be addressed. As transistors become smaller, the complexity of manufacturing them increases, leading to higher defect rates and reduced yields. This, in turn, drives up the cost of production, making it less economically viable to continue shrinking transistors. Furthermore, the increased difficulty in testing and validating the functionality of smaller devices also increases the cost and time required for development.

The impact of quantum effects on transistor behavior is another major challenge that needs to be addressed. At atomic scales, quantum tunnelling causes electrons to pass through insulating barriers that are supposed to isolate different components of the transistor, leading to uncontrolled current flow and making precise control difficult. This unpredictability in device operation also makes it harder to maintain the reliability and consistency that Moore's Law historically depended on.

MIT's 3D Layers Challenge Atomic Challenges

In a recent achievement, researchers from the Massachusetts Institute of Technology (MIT) have successfully developed a method for stacking electronic layers to create faster, denser, and more powerful computer chips. The new technology, which has the potential to exponentially boost the number of transistors on chips, could pave the way for more efficient AI hardware and reshape the electronics industry.

This breakthrough aligns with ongoing efforts in semiconductor innovation, such as monolithic 3D integration techniques demonstrated in studies like the one published in Nature. By addressing traditional silicon's limitations, including issues like heat dissipation and interconnect delays, MIT's method could redefine the scalability of computing hardware, paving the way for applications beyond AI, including edge computing and next-generation IoT devices.

Breakthrough in Stacking Semiconducting Materials

The researchers, led by Associate Professor Jeehwan Kim of Mechanical Engineering at MIT, have developed a method for stacking high-quality semiconducting materials on top of each other without the need for thick silicon wafer substrates. This allows for multiple layers of semiconducting materials to be in direct contact, enabling faster communication and computation between layers.

Moreover, the method's ability to operate at lower temperatures (below 400°C) makes it compatible with existing silicon-based transistor circuits, a critical advancement when compared to conventional fabrication techniques. The growth of single-crystalline 2D materials on amorphous surfaces at such temperatures eliminates prior bottlenecks in semiconductor manufacturing, allowing seamless integration with mature technologies without compromising performance.

Transforming AI and Data Processing

According to Kim, the new method could lead to orders-of-magnitude improvements in computing power for applications in AI, logic, and memory. The researchers envision that the method could be used to build AI hardware, such as stacked chips for laptops or wearable devices, that would be as fast and powerful as today's supercomputers and could store huge amounts of data comparable to physical data centres.

This innovation mirrors the structural shift seen in high-rise 3D chips developed at MIT, where multilayered transistors and logic circuits are engineered to bypass silicon wafers. Such designs effectively double transistor density, enhancing vertical data processing speeds crucial for modern computing tasks like machine learning, large-scale simulations, and quantum modelling.

Revolutionising Semiconductor Growth

The study, published in the journal Nature, describes how the researchers developed a method for growing single-crystalline 2D materials at temperatures as low as 380 degrees Celsius, which is considerably lower than the temperatures required for traditional semiconductor growth. The researchers used a mask of silicon dioxide to pattern the growth of single-crystalline materials, which was then deposited onto a silicon wafer that already had transistor circuitry.

This low-temperature capability not only reduces energy consumption but also minimises thermal stresses on components, making the process highly efficient and sustainable. Studies have shown that this approach mitigates issues like lattice mismatch, which traditionally hamper the growth of high-quality semiconductors on heterogeneous substrates.

Advances in TMD Integration

The team was able to grow two different TMDs - molybdenum disulfide and tungsten diselenide - in single-crystalline form, directly on top of each other, without requiring any intermediate silicon wafers. Kim noted that the method will effectively double the density of a chip's semiconducting elements, particularly in Metal-Oxide Semiconductor (MOS) technology, which is a basic building block of modern logic circuitry.

This breakthrough supports advancements in complementary technologies, such as dynamic memory integration and logic gates, ensuring that high-performance computing platforms remain compact while exponentially increasing their computational capacity. Recent developments in the field have highlighted the compatibility of such designs with flexible electronics, offering new possibilities for wearable technologies.

Demonstrating Multilayered Chip Potential

The researchers have already demonstrated the capabilities of their new method by fabricating a multilayered chip with alternating layers of the two TMDs. The chip was able to communicate effectively between the different layers, demonstrating the potential of the new technology.

In addition to the alternating layers of TMDs, the adoption of edge nucleation techniques, a principle borrowed from metallurgy, ensures uniform crystalline growth. This innovation allows for consistent layer alignment, critical for minimising data latency and enhancing cross-layer communication in multilayered chips.

While the researchers have already demonstrated the capabilities of their new method, there are still challenges that need to be addressed before it can be commercialised. One of the main challenges is scaling up the production process to create larger chips that can handle more complex tasks. The researchers have already started working on this, but more research is needed to fully realise the potential of the new technology.

Future Research and Industrial Applications

Future research directions may focus on scaling these processes for industrial applications, with collaborations between institutions and private stakeholders being key to accelerating deployment. For instance, the introduction of nanoscale trench structures and improved deposition techniques could enable the fabrication of even more complex chip architectures, fulfilling growing demands for high-performance computing solutions.

Could 3D Stacked Devices Help Continue Moore's Law

The introduction of 3D stacked devices has the potential to significantly enhance the performance and efficiency of semiconductors. One of the main advantages of 3D stacked devices is that they can integrate multiple layers of transistors, which allows for increased processing power while reducing the overall size of the chip. This is particularly beneficial for complex applications such as artificial intelligence and machine learning, which require large amounts of processing power.

In addition to increased processing power, 3D stacked devices also offer faster communication between layers, which can result in reduced latency. This is especially important for applications that require fast data transfer rates, such as data centres and cloud computing platforms. Furthermore, the use of 3D stacked devices can also improve energy efficiency by reducing the need for external communication between different layers. This can result in significant energy savings, which can be particularly beneficial for mobile devices that require long battery life.

Revolutionising Semiconductor Design

The introduction of 3D stacked devices has the potential to revolutionise the semiconductor industry in a number of ways. One of the main advantages of 3D stacked devices is that they can maximise chip space and integrate multiple semiconductors onto a single chip. This can result in significant cost savings for manufacturers, as well as reducing the overall size of the chip. At the same time, the use of 3D stacked devices can also reduce the complexity of chip design, which can result in faster development times and lower costs.

Another potential benefit of 3D stacked devices is that they can be used to specialise in applications such as AI. As AI continues to become increasingly important in modern technology, the need for high-performance computing platforms that can handle complex AI algorithms is growing. The use of 3D stacked devices can provide a high-performance computing platform that is specifically designed for AI applications, which can result in faster development times and lower costs.

MIT’s Vision for 3D Stacked Devices

MIT's 3D stacking method is an exciting prospect for the future of computing. It provides a means to continue the progress of Moore's Law at a time when traditional methods have reached their limits. By enabling higher transistor densities, improving energy efficiency, and enhancing performance, MIT's 3D stacked devices offer a clear path forward for the semiconductor industry.

Future Impacts on Computing

As we move into a future driven by artificial intelligence, machine learning, and big data, the demand for more powerful and efficient computing will only increase. MIT's approach offers a way to meet this demand while also preserving the underlying principles that have driven technological growth for decades. If successfully commercialised, 3D stacking could play a critical role in shaping the next generation of computing devices, ensuring that Moore's Law, in some form, remains relevant for years to come.

In conclusion, MIT's development of 3D stacked devices represents a significant breakthrough in semiconductor technology. While it may not be the only answer to continuing Moore's Law, it is undoubtedly a powerful candidate — one that could unlock new realms of computing potential, transforming industries and advancing technology in ways that were previously unimaginable.