Unisantis Unveils Dynamic Flash Memory

01-06-2021 | By Sam Brown

Recently, South Korean tech company Unisantis unveiled a new memory technology called Dynamic Flash Memory at the virtual IEEE International Memory Workshop. So what challenges does DRAM face, what is Dynamic Flash, and could it replace DRAM?

What challenges does DRAM face?

Dynamic Random Access Memory, or DRAM for short, is a memory technology that plays a critical role in modern computer architecture. High-speed memory such as SRAM is ideal for cache and registers on a CPU but is not ideal for large memories (i.e. those that exceed a few megabytes) due to its physical size. Hard drives are ideal for storing large amounts of data, but cannot be used for storing running programs as their access time is too long. DRAM, however, is small in its construction (only a single transistor and capacitor per bit) and offers high-speed access thereby making it ideal for holding running applications.

However, even DRAM has its drawbacks with some including the need to constantly refresh the memory (as the capacitors discharge over time), and the destructive nature of its read cycle. The volatile nature of DRAM also sees its information lost as soon as power is interrupted, and this makes DRAM far from ideal for storing any long-term data.

What is Dynamic Flash Memory?

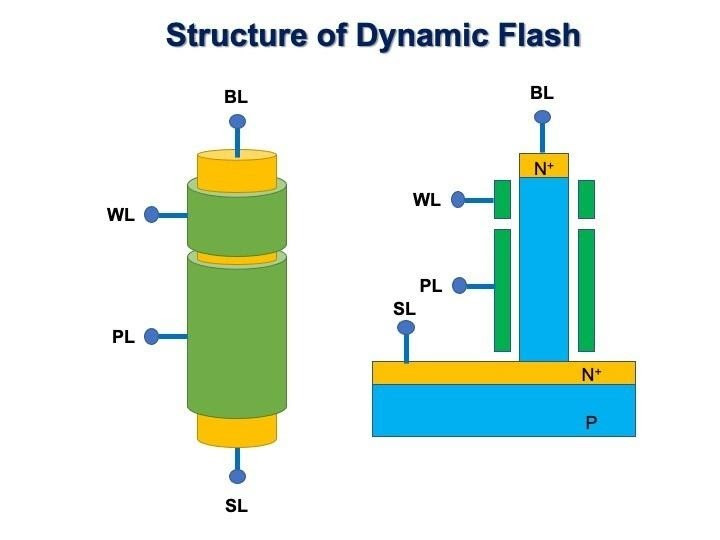

Recently, Unisantis unveiled its latest memory technology called Dynamic Flash Memory, or DFM for short, and claims that this memory technology could replace DRAM in the near future. Unlike DRAM which uses capacitors to store charge, DFM uses a single vertical transistor that has two separate gates that encircle the channel.

The resulting 3D transistor is able to store information, albeit volatile, and has a significantly higher density than that of DRAM. While DRAM has an expected upper memory limit of 16Gb, the use of TCAD simulation shows that DFM can multiply this by 4.

The designers of the new memory state that DFM does not rely on a capacitor and as such has fewer leakage points. In addition, the new memory technology, being a Flash memory, can also offer block erase and block refresh which reduces the frequency of refresh cycles.

What remains unclear around DFM?

Despite the many press releases on DFM, one question remains to be answered; how exactly does this new device store bits? The announcement from Unisantis states that the memory is volatile, thus meaning that it will lose its state when powered off, but then also refer to Flash memory, meaning that it uses quantum tunnelling to trap charges.

Authors Opinion

From what has been said, it appears that the new memory cell operates by trapping charge in its channel in a similar fashion to a floating gate. However, trapping charge onto a floating gate requires a large voltage, and the tunnelling electrons effectively degrade the transistor structure. In the new 3D structure developed by Unisantis, charges are not being stored on a gate, but instead in the channel itself.

The program line to the transistor structure covers most channels, and when this is activated, charges can flow from the source line to the bit line. When the program line is deactivated, any charges in the channel are trapped. When the bit is to be read, the world line is activated, but the word gate is much smaller than the program gate. As such, activating the word line only causes a current to flow if the charge is already on the channel. If there is a charge in the channel, then the very act of reading recharges the cell (hence non-destructive reading). If there is no charge in the channel, then no current flows through, and this is also non-destructive.

Credit: Unisantis

Read More